Fujitsu announced that its invention for accelerating scientific computing has been awarded the prestigious Japan Patent Office Commissioner’s Award at the 2024 Kanto Regional Commendation for Invention, presented by the Japan Institute of Invention and Innovation (JIII) (1) on November 1, 2024.

The award-winning invention, developed by Fujitsu in 2009, enables high-speed and high-precision scientific computing. The technology has made a significant contribution to the industry worldwide through its utilization in the K computer and the supercomputer Fugaku , jointly developed with RIKEN and Fujitsu, as well as in Arm®-based server products.

Overview

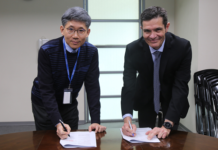

1. Award recipients (2):

Japan Patent Office Commissioner’s Award: Mikio Hondou, Fujitsu Limited

Invention Implementation Merit Award (3): Takahito Tokita, Representative Director, CEO, Fujitsu Limited

2. Invention title:

Invention of a Computing Device that Accelerates Scientific Calculations (4)

3. About the award-winning invention:

(1) Features of the invention

This award-winning invention enables the high-speed processing of mathematical functions crucial for scientific computing (Figure 1). It successfully reduced the number of instructions required for preprocessing the Taylor series expansion (5) to 1/3 (Figure 2) by defining special instructions that can be sped up while minimizing the increase in circuit scale. As a result, both the speed of calculation processing and the accuracy of calculation are maintained.

(2) Industrial applicationsThis invention enables faster and more accurate execution of supercomputer operations including structural analysis, collision analysis, and fluid analysis simulations for automobiles and aircraft, as well as simulations of global environmental predictions, earthquakes, and tsunamis. This contributes to industrial development and the creation of a safer society.

This technology was implemented in the K computer and Fugaku, and is now a standard feature (6) in the instruction set architecture designed and licensed by Arm, a leading compute platform company. Its inclusion in Arm-based server products used by hyperscalers has generated significant international impact. This technology is also slated for inclusion in “FUJITSU-MONAKA”, Fujitsu‘s next-generation processor for data centers, targeted for launch in 2027.

(1) Japan Institute of Invention and Innovation (JIII) :Located in Minato-ku, Tokyo; Chairman: Takeshi Uchiyamada

(2) Award recipients :Affiliations reflect those at the time of application.

(3)Invention Implementation Merit Award :An award for the representative of a company or organization that supported the completion of a highly advanced invention.

(4) Invention of a Computing Device that Accelerates Scientific Calculations :Patent No. 5304483, filed in 2009 and registered in 2013.

(5) Taylor series expansion :A calculation method for calculating trigonometric functions such as sin and cos, and exponential and logarithmic functions such as exp and log.

(6) Standard feature :Initially adopted in the Armv8 SIMD extension specification SVE, and subsequently adopted as a standard in the latest Armv9 SVE/SVE2.