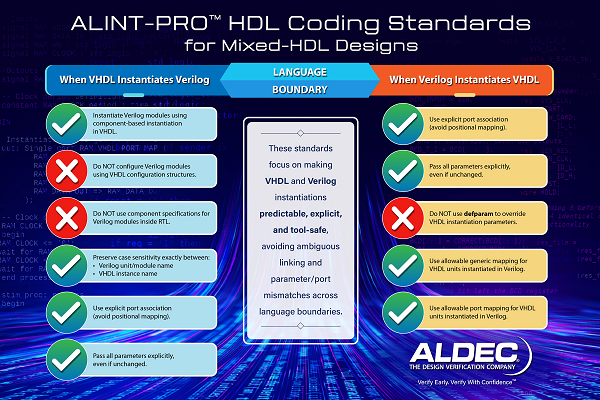

Aldec, Inc., a pioneer in mixed HDL language simulation and verification solutions for FPGA and ASIC designs, announced the availability of ALINT-PRO 2025.12, delivering a new set of design rules and guidance for mixed-language projects. The update helps engineering teams improve correctness, maintainability, and IP interoperability when combining VHDL and Verilog/SystemVerilog within a single project.

As mixed-language development becomes increasingly common for IP reuse, third-party integration, and long-life product maintenance, design teams face challenges caused by ambiguous mapping, inconsistent parameter passing, and configuration misuse. ALINT-PRO 2025.12 reduces these risks with a focused set of best-practice rules aimed at preventing integration issues before simulation, synthesis, and downstream verification.

“Mixed-language design is a reality for most FPGA and ASIC teams, but small instantiation and mapping inconsistencies can create time-consuming debug cycles,” said Louie De Luna, Chief Marketing Officer at Aldec. “With ALINT-PRO 2025.12, we’re providing designers with clear, enforceable rules that reduce ambiguity and improve predictability when VHDL and Verilog live in the same project.”

New Mixed-Language Design Rules in ALINT-PRO 2025.12 Premium Rule Library

The new ALINT-PRO 2025.12 rules establish a consistent methodology for module/entity instantiation across language boundaries. The rules are:

Verilog Module Instantiation in VHDL

- Use the component-based instantiation method for Verilog module instances in VHDL.

- Do not configure Verilog modules in VHDL configuration structures.

- Do not use component specifications for Verilog modules in RTL descriptions.

- Preserve case sensitivity between the Verilog unit name and its VHDL instance name.

- Use explicit port association for Verilog unit instantiations in VHDL.

- Pass all parameters to Verilog unit instantiations in VHDL, even if they are unchanged.

VHDL Unit Instantiation in Verilog

- Use explicit port association for VHDL unit instantiations in Verilog.

- Pass all parameters to VHDL unit instantiations in Verilog, even if they are unchanged.

- Do not use defparam for overriding VHDL instantiation parameters in Verilog.

- Use allowable generic mapping for VHDL units instantiated in Verilog.

- Use allowable port mapping for VHDL units instantiated in Verilog.

These rules are designed to reduce cross-language interpretation differences, ensure consistent elaboration behavior, and make design intent explicit, thus improving mixed-language integration success across simulation, linting, and synthesis flows.

Availability

ALINT-PRO 2025.12 is available immediately. Current users can access the update through Aldec support channels and product delivery mechanisms. Also, parties interested in evaluating the new mixed-language capabilities, as well as ALINT-PRO’s extensive static verification capabilities, can request a fully functional evaluation version of the tool.

ALINT-PRO 2025.12 is now available for download and evaluation.