Analog Bits’ Analog and Mixed Signal IPs Including Various PLLs, PCIe Reference Clock, Sensors and Power Circuits with GLOBALFOUNDRIES 12nm FinFET (12LP) Enable Customers Lowest System Level Cost & Power

Analog Bits analog and mixed signal IP design kit is available for GLOBALFOUNDRIES 12nm FinFET to meet customer’s processing needs for compute-intensive applications. Through collaboration with GF, the IP portfolio includes wide range fractional Phase-Lock Loop (PLL) with Spread Spectrum Clock Generation (SSCG), PCIe reference clock PLL subsystem, Process, Voltage, and Temperature (PVT) Sensor and Power-On-Reset (POR) circuitry. Silicon Reports based on these IPs will be available 2Q 2020, and first customer tape-out is expected in 2H 2020.

GF’s 12LP technology is specifically designed to deliver the ultra-high performance and data-processing capacity customers need to support their Compute, Connect and Storage (CCS), AI/ML, high-end consumer and automotive solutions in the era of big data and cognitive computing. The technology, which delivers a 10 percent improvement in logic density and more than a 15 percent improvement in performance compared to the previous FinFET generation, includes new market-focused features specifically designed for automotive electronics and RF/analog applications.

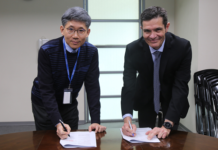

“GF continues to see growing demand for feature rich offerings driven by AI and 5G. Analog and mixed signal IP combined with our 12LP technology offers our customers the differentiated process design creation to address these demands,” said Mark Ireland, vice president of ecosystem partnerships at GF. “By collaborating closely with Analog Bits we are enabling our mutual customers to integrate all IP blocks to reach the target Performance, Power, and Area (PPA) for system level integration and deliver differentiated end products for a broad set of market segments.”

“The analog and mixed signal IP is the knowledge and insight from 20 years working with tier-one semiconductor design teams to understand their needs at the system level,” said Mahesh Tirupattur, executive vice president at Analog Bits. “Our close collaboration with GF gives us the opportunity to help our mutual customers deliver the best possible PPA. We truly appreciate our years of strategic partnership with GF.”Join Analog Bits and GLOBALFOUNDRIES at Design Automation Conference in Las Vegas, Nevada on June 3rd to learn more about the 12LP process technology solution